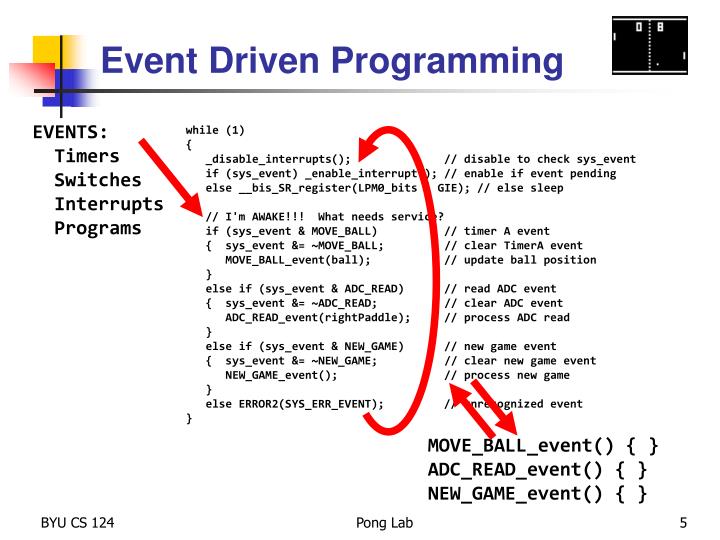

The internal pullup for each pin is used to hold the pin high, and a high-to-low transition on the pin triggers. Each button is connected to a GPIO pin and an interrupt is used for each input to determine whether the user has pressed that button.

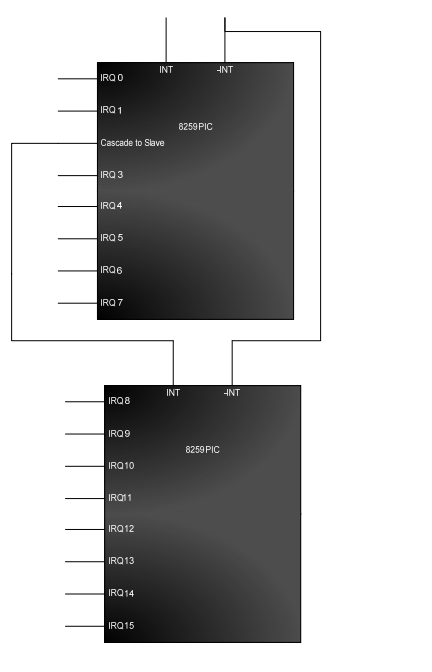

Libopencm3 Cortex Nested Vectored Interrupt Controller Version 1.0.0 Author © 2010 Thomas Otto tommi 2012 Fergus Noble fergu Date 18 August 2012Ĭortex processors provide 14 cortex-defined interrupts (NMI, usage faults, systicks etc.) and varying numbers of implementation defined interrupts (typically peripherial interrupts and DMA). The PRUSS interrupt controller (INTC) is an hardware interface between interrupts coming from different parts of the system (these are referred to as system events), and the PRUs interrupt inputs. I have a device that has several buttons. Nvic_set_priority (uint8_t irqn, uint8_t priority)

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed